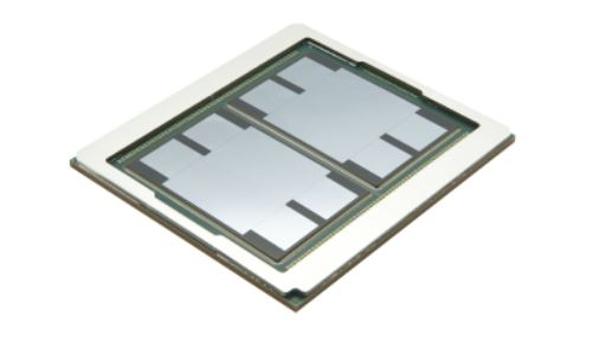

ASE has developed a 70×78-mm Fan-Out Chip on Substrate Bridge (FOCoS-Bridge) package that packs two ASICs and eight high-bandwidth memory devices connected via eight silicon bridges. The large package integrates two identical 47×31-mm FOCoS-Bridge structures side-by-side, each with one ASIC and four high-bandwidth memory devices and four silicon bridges.

FOCoS-Bridge technology is highly scalable, enabling seamless integration into complex chiplet architectures used in high-performance computing and artificial intelligence applications. It provides high-density die-to-die connections, high I/O counts, and fast signal transmission. The use of a silicon bridge die achieves a die edge linear density (wire/mm/layer) that is an order of magnitude higher than a conventional organic flip-chip package.

ASE expects the FOCoS-Bridge technology to establish a foundation for embedding passives and active chips in the fan-out package. By overcoming the limitations of conventional electrical interconnects, the FOCoS-Bridge permits high-speed, low-latency, and energy-efficient data communication between processors, accelerators, and memory modules.

FOCoS-Bridge is one of the six core packaging technologies of the ASE VIPack platform, supported by a co-design ecosystem.

Advanced Semiconductor Engineering

Find more datasheets on products like this one at Datasheets.com, searchable by category, part #, description, manufacturer, and more.