Silicon carbide (SiC) has arrived, and it’s a big deal. It was written all over APEC 2023 show with a string attached: the cost of a SiC device is significantly higher than its silicon counterpart. Several seminars and keynotes about SiC provided first-hand details about the cost issues and what the industry is doing to address them.

At his keynote titled “Silicon Carbide Mass Commercialization and Future Trends” at APEC 2023, Victor Veliadis, executive director and CTO at Power America, outlined wafer cost, defects, scalability of the device area, reliability, and ruggedness concerns as major barriers for SiC in next-generation power electronics. Power America is a member-driven consortium of industry, universities, and national labs.

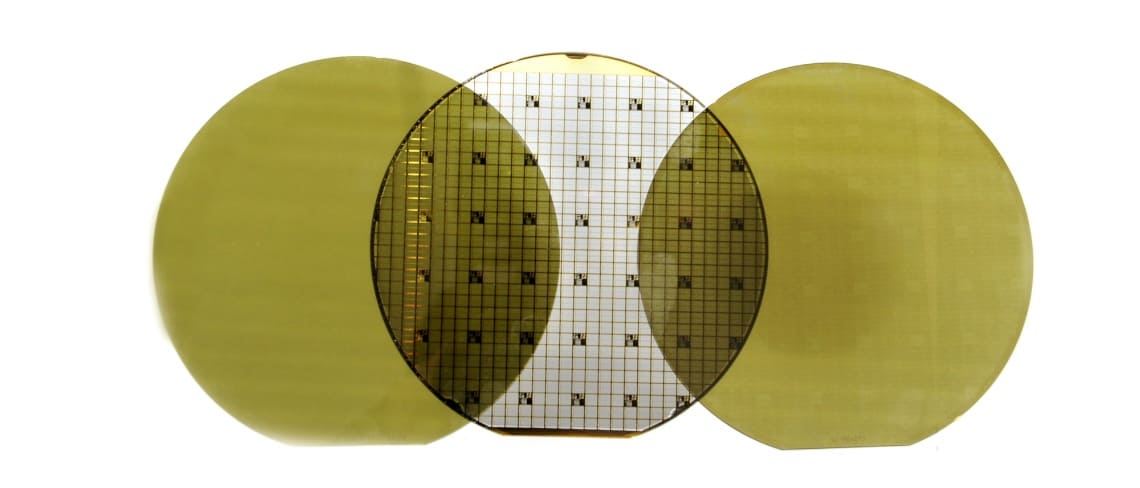

“The commercially available manufacturing processes for silicon are streamlined and high yield,” Veliadis said. “In SiC, you need processes that are SiC specific because it’s a very hard material.” That makes SiC wafers—currently moving from 150 mm to 200 mm—highly complex. “More complexity inevitably leads to higher cost,” he added.

While emphasizing the need for new fab models and a vibrant SiC manufacturing infrastructure, he proposed using old equipment manufacturing silicon devices complemented by SiC-specific tools. “Process SiC in silicon fabs while using 30-year-old equipment by adding SiC-specific tools and explore the silicon economy of scale.”

Figure 1 Victor Veliadis highlighted the need for new fab models and manufacturing infrastructure for SiC in his keynote at APEC 2023.

Narrowing down to the most crucial issue—cost—Veliadis claimed that 40% to 60% of SiC device cost relates to the substrate. “Wafer substrate complexity is the key factor in higher than silicon device cost,” he added. That explains why several major SiC players like STMicroelectronics and onsemi are proactively bolstering SiC wafer supply.

Vertical integration is back

STMicroelectronics, very prominent on this front, first acquired Sweden-based SiC wafer supplier Norstel and then deepened its cooperation with French material supplier Soitec for its SiC substrate technology. Soitec is among the early suppliers offering 200-mm SiC wafers.

Moreover, to ramp up its production of SiC devices, ST is building a new fab in Catania, Italy, which is dedicated to SiC devices. Besides its front-end fabs in Catania, Italy and Ang Mo Kio, Singapore, ST has back-end facilities for assembly and testing in Shenzhen, China and Bouskoura, Morocco. Next, ST has started small-volume 150-mm production for substrate manufacturing in Norrkoping, Sweden. Here, it’s also experimenting with 200-mm prototypes to enhance wafer quality and yield.

At APEC, while talking about ST’s focus on SiC wafer management, Gianluca Aureliano, Americas marketing manager for automotive power transistors at STMicroelectronics, acknowledged the complexity of building SiC wafers and related defect issues. “Dedicated machines for SiC fabrication can lead to extra cost,” he said. “It’s a new material, so material cost is a significant factor.”

Figure 2 Vertical integration is making a comeback in the SiC technology realm. Source: Yole

Five years after inheriting the SiC business from Fairchild Semiconductor and turning SiC into a strategic bet for automotive and industrial markets, onsemi snapped GT Advanced Technologies (GTAT), a supplier of SiC materials in New Hampshire. It’s worth mentioning here that Fairchild had bought Swedish startup TranSiC to enter the SiC market before it was acquired by onsemi in 2016.

Also, onsemi as well as Infineon had SiC wafer supply agreements with GTAT before onsemi acquired GTAT in a $415 million cash deal to bolster its supply of competitive SiC wafers. Now, onsemi plans to expand GTAT’s SiC crystal growth technology into 150-mm and 200-mm wafer realms.

Epi layer cost

Peter Friedrichs, senior director for wide bandgap at Infineon Technologies, acknowledged that wafer is a major cost point in SiC devices. However, resonating with Veliadis’ views, he noted that front-end SiC manufacturing isn’t much different from silicon-based IGBTs. “That opens the door for using silicon fabs with specialized SiC tools.”

Friedrichs also noted that the epitaxial process mainly constitutes the cost. SiC epi-wafers are produced through deposition and growth of epitaxial SiC layer on the surface of single-crystal SiC substrate.

“Epi requires demanding tools that are also expensive,” he added. Infineon has adopted a multi-source approach for SiC substrates to counter the wafer cost. Here, it’s worth noting that wafer suppliers like Resonac now offer tools that prevent the expansion of dislocation defects existing in SiC substrate into the epitaxial SiC layer.

Figure 3 Infineon has signed a multi-year SiC wafer supply deal with Resonac, formerly known as Showa Denko. Source: Infineon

Friedrichs and Veliadis agree on another key premise: high SiC devices cost can be compensated by reducing the overall cost at the system level. “Lower system cost can be achieved with the reduced amount of magnetics at higher frequency and simplified thermal management,” Veliadis said in his keynote.

Besides cost, wafer defects are a major headache in SiC device manufacturing. “The presence of defects limits the scalability of the device area,” said Veliadis. “To minimize defects, engineers must get threshold stability under control.” Thus, engineers can make larger-area devices by reducing defects.

SiC device ruggedness, another crucial issue, relates to high avalanche tolerance. “SiC circuit ruggedness is enabled by fast gate drives with protection features,” Veliadis said. That shows a way forward and that challenges will be overcome over time.

With greater focus on SiC crystal growth, epitaxial layer and robust wafer supply, the component cost of SiC is expected to come down over time. Though challenges are real, stakes are too high for the status quo to hold SiC progress hostage for long.

Related Content